Tao Wang Nijmegen FASTER Meeting, Sep 24th, 2025

# HGTD Calibration Overview

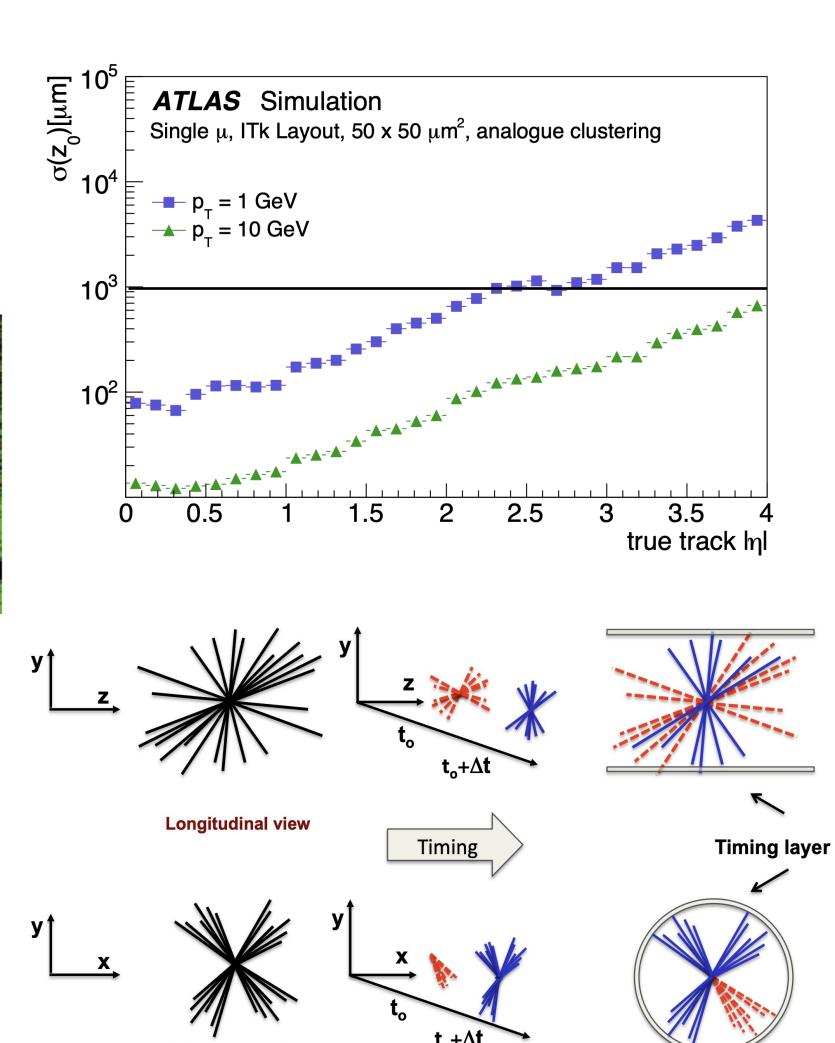

#### Motivation

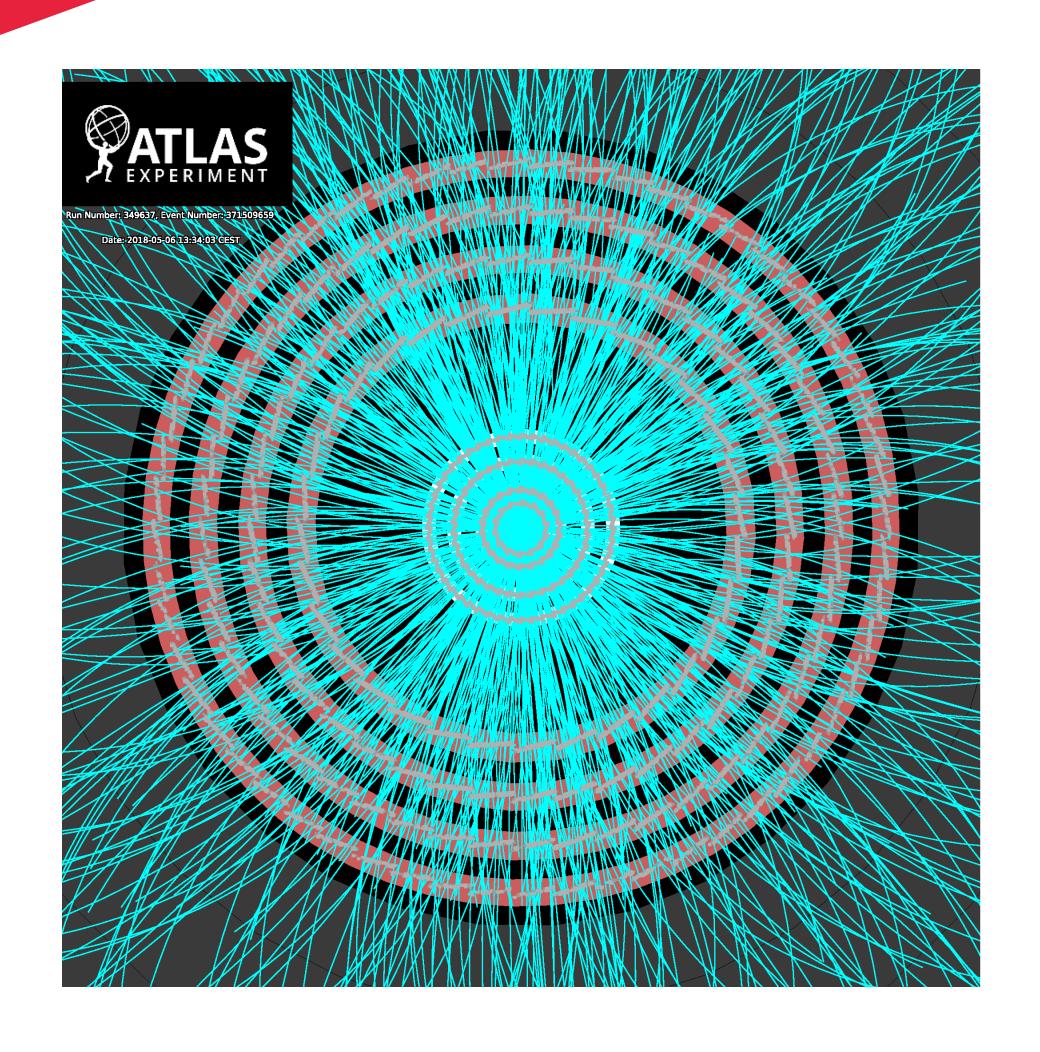

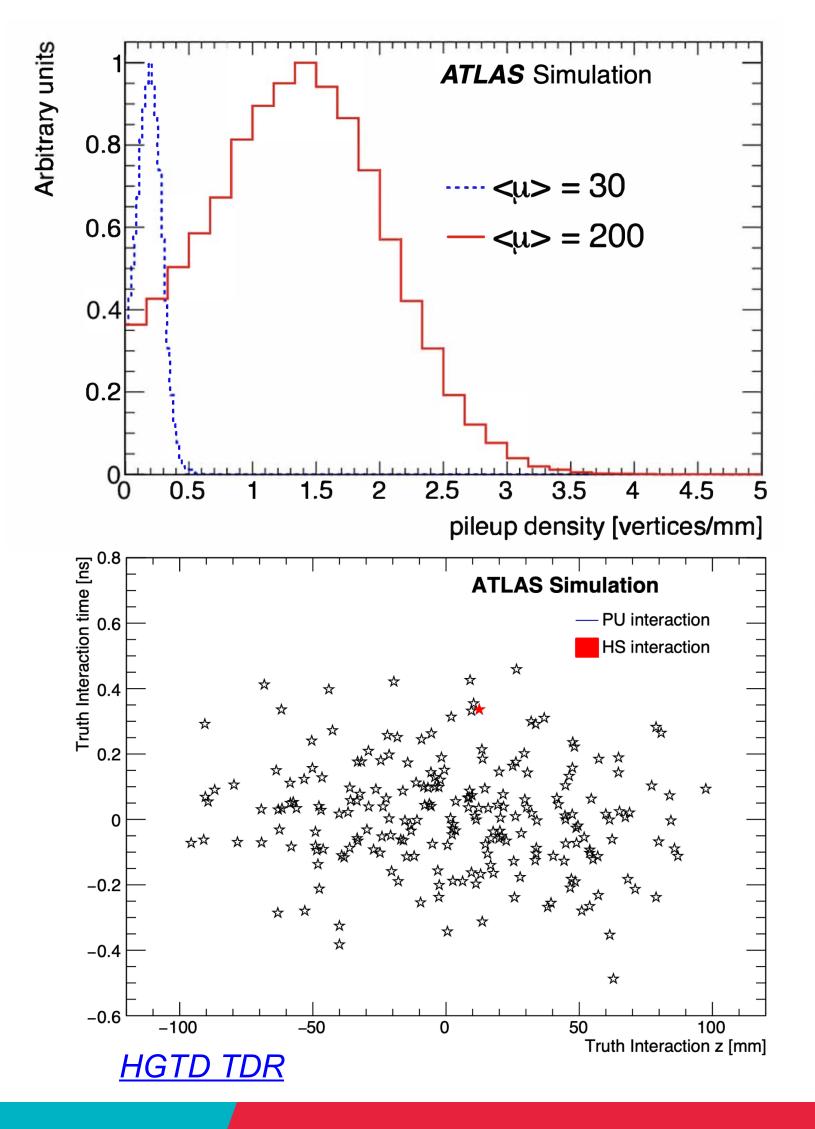

### HL-LHC

<u>1704.08666</u>

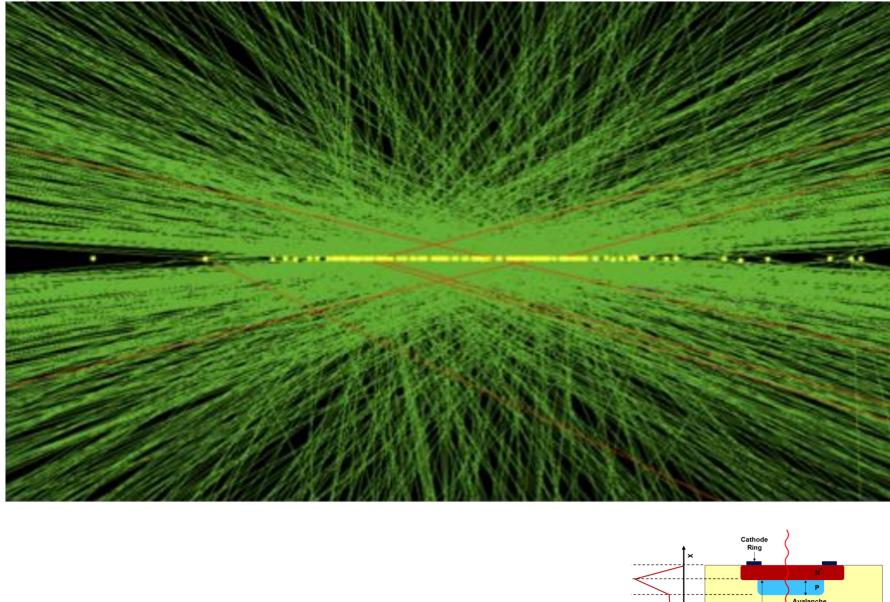

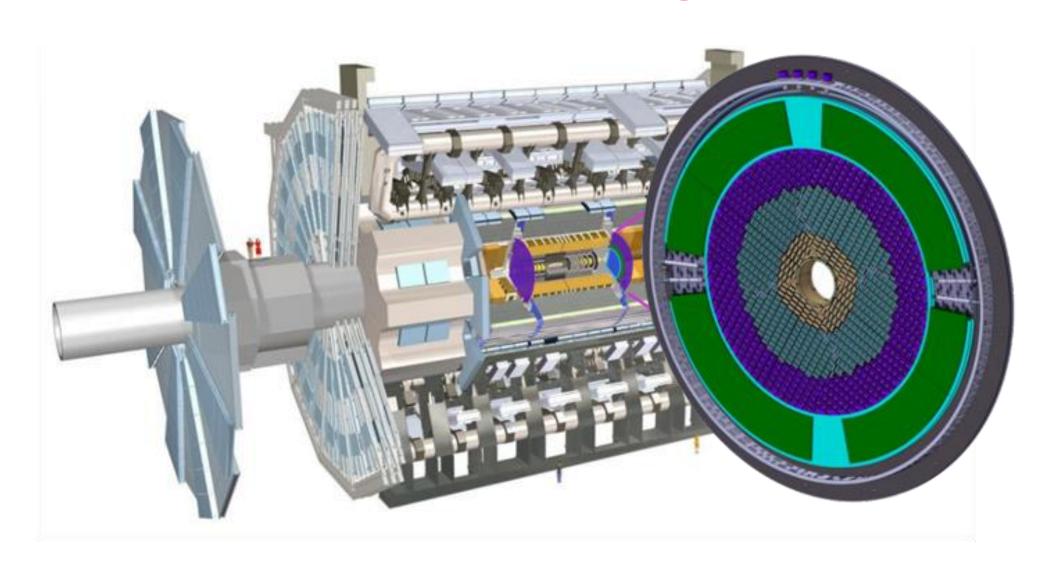

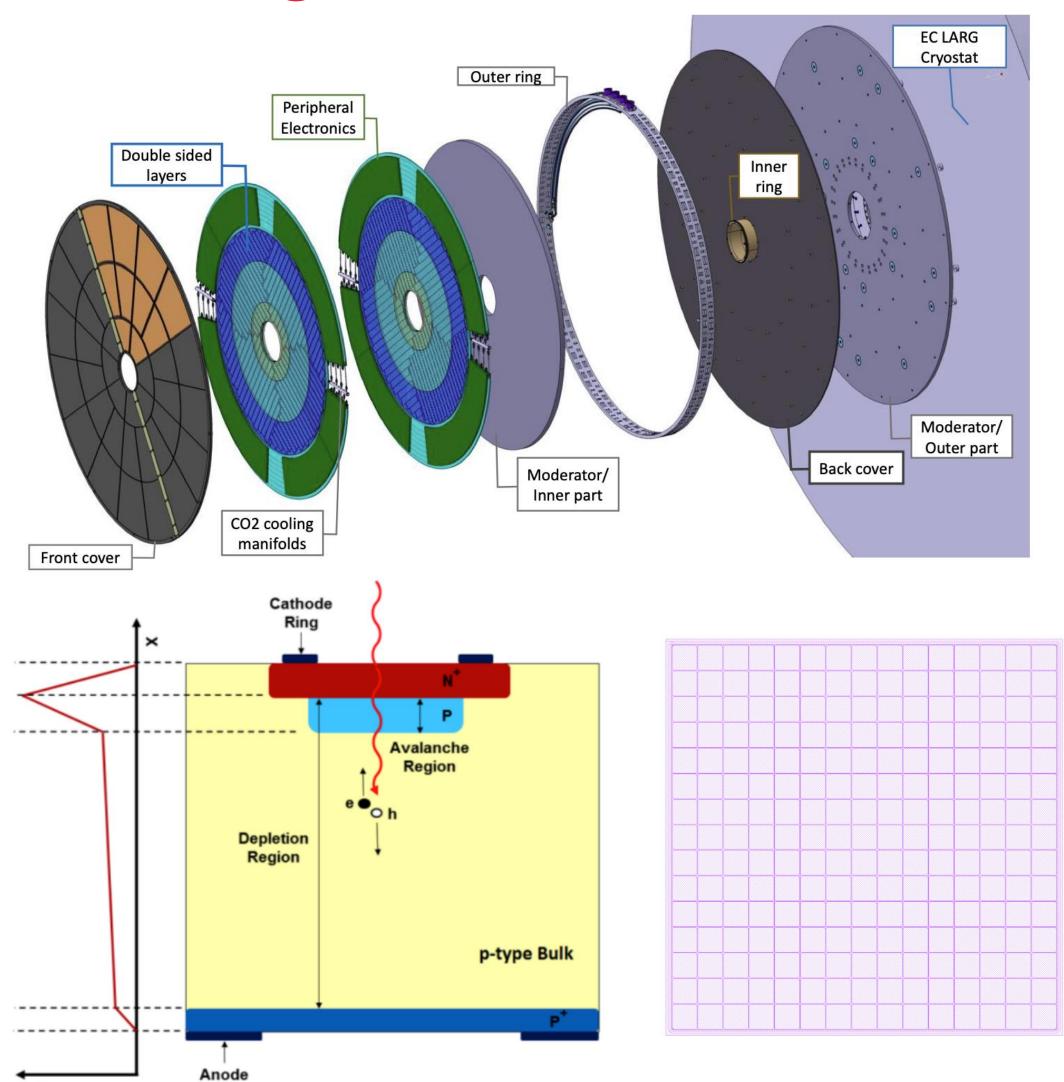

## Introduction to High Granularity Timing Detector

- 2 double sided layers at  $z=\pm 3500$  mm, covering  $2.4 < |\eta| < 4.0$

- Operating temperature -30 °C

- Time resolution: 35 ps (start) 70 ps (end)

- Low Gain Avalanche Detector technology is used

- 15x15 pads

- Pad size: 1.3 mmx1.3 mm

- Thickness: 775 μm (physical)/50 μm (active)

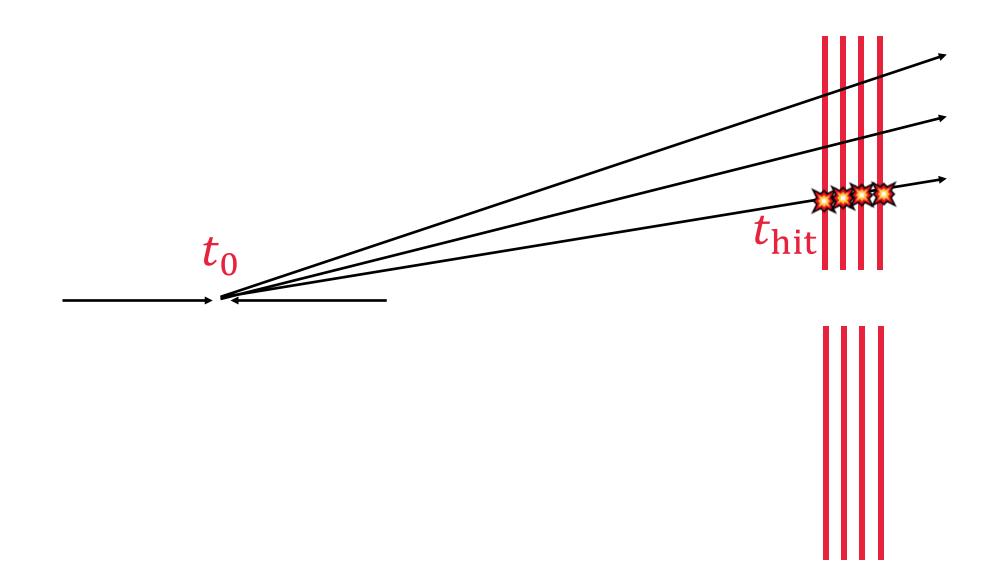

#### Calibration

#### thit

$$\sigma_{\text{total}}^2 = \sigma_{\text{Landau}}^2 + \sigma_{\text{Timewalk}}^2 + \sigma_{\text{Jitter}}^2 + \sigma_{\text{TDC}}^2 + \sigma_{\text{Clock}}^2$$

$$\frac{1704.08666}{6}$$

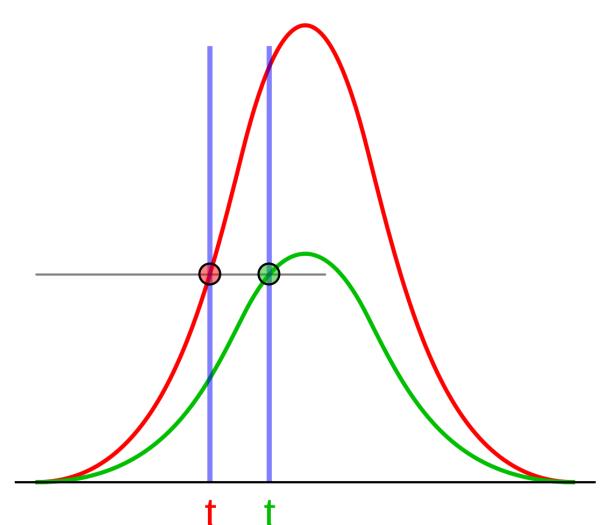

- $\sigma_{

m Timewalk}$ : the  $t_{

m TOA}$  will depends on the signal amplitude if constant threshold triggering is used, can be corrected using  $t_{

m TOT}$

- $\sigma_{\rm TDC}$ : relates to TDC binning and non-linearity, expected to be  $\geq 20~{\rm ps}/\sqrt{12}$

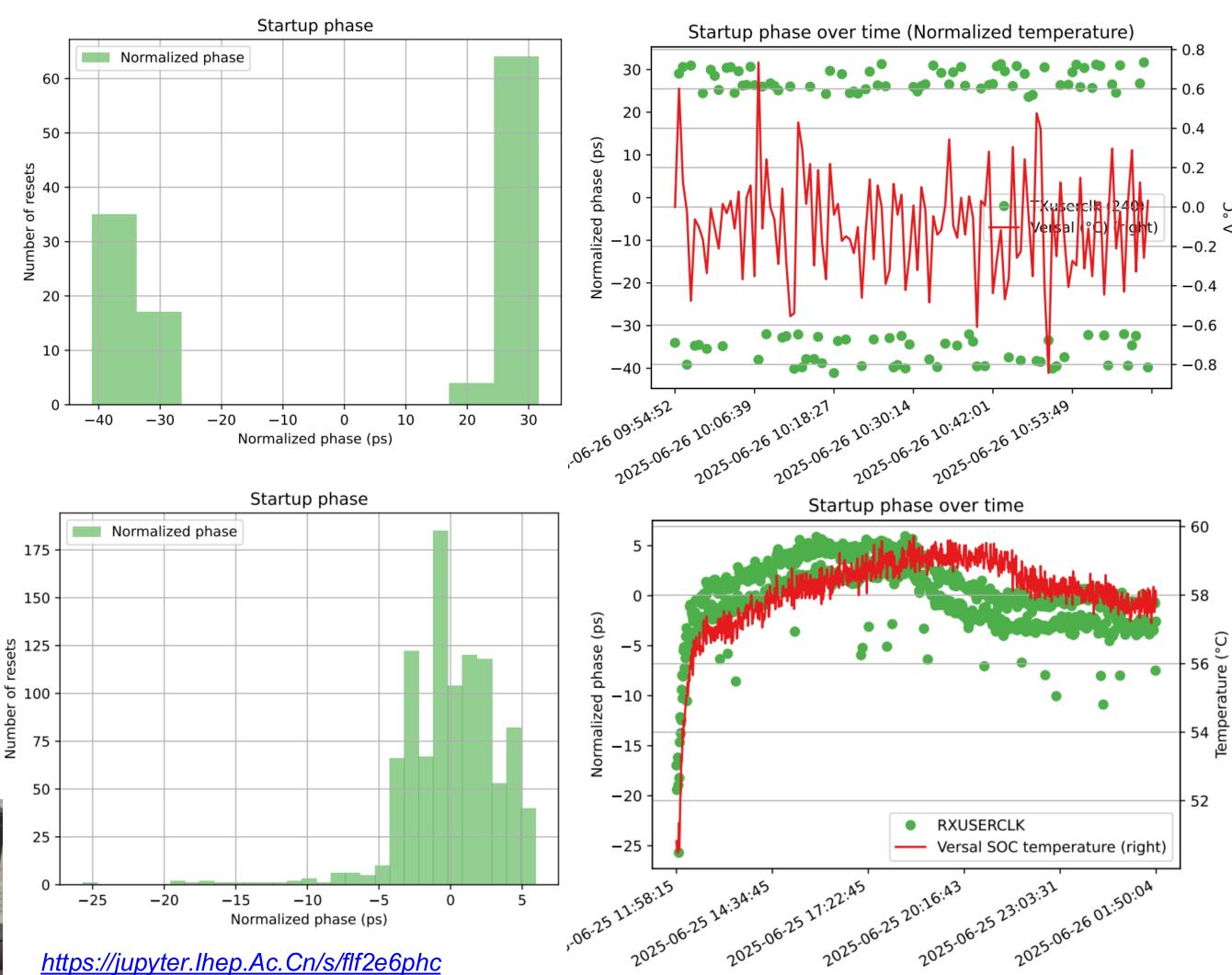

- $\sigma_{\rm Clock}$ : relates to the jitter of the 40MHz clock, expected to be < 15 ps after calibration

#### $t_0$

• Correspond to the bunch crossing time. The different HGTD hits in one event should give the same  $t_0$ , which must be calibrated

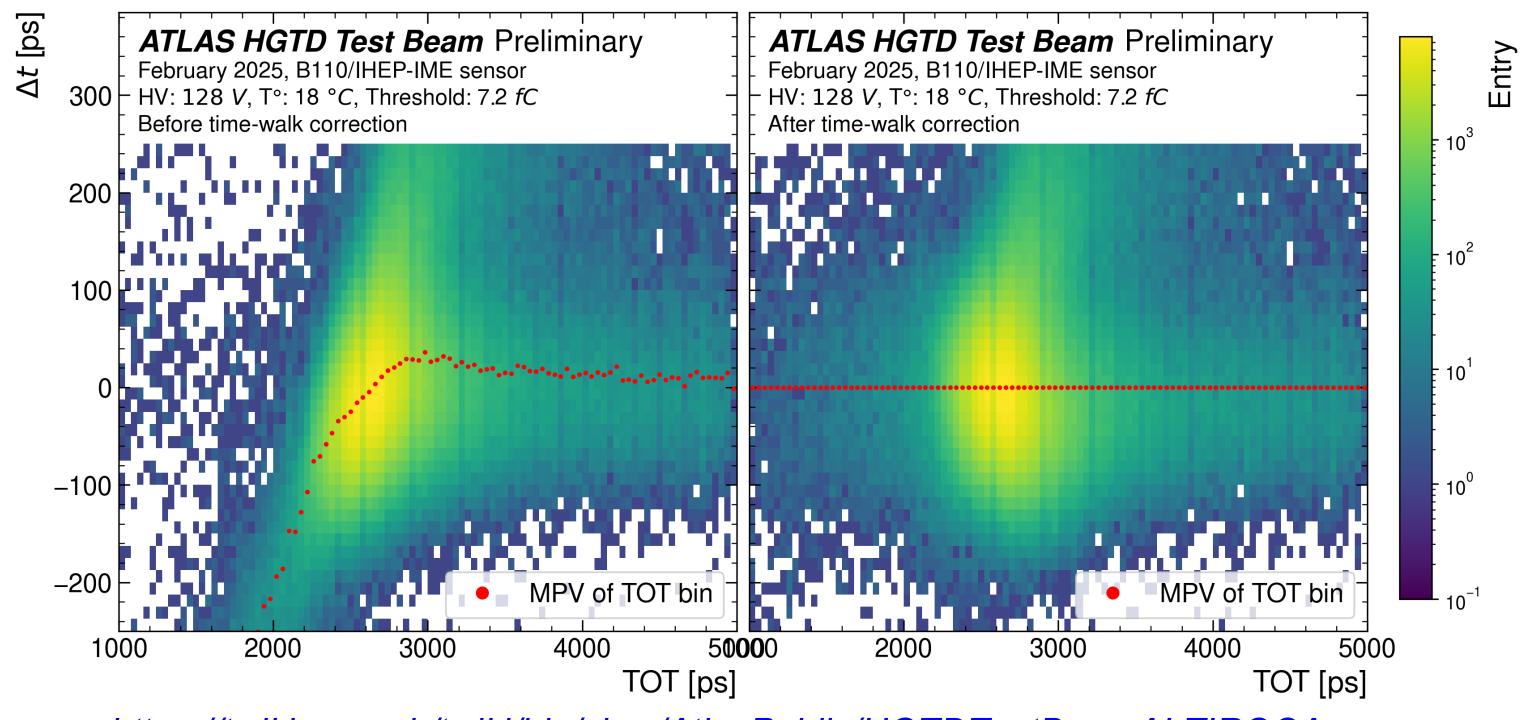

#### Time Walk Calibration

- When the constant threshold is used to determine TOA, the TOA will vary according to the pulse height

- The TOT also correlates with the pulse height, and can be used to correct the time walk effect

https://twiki.cern.ch/twiki/bin/view/AtlasPublic/HGTDTestBeamALTIROCA

The time walk effect is largely reduced after the correction

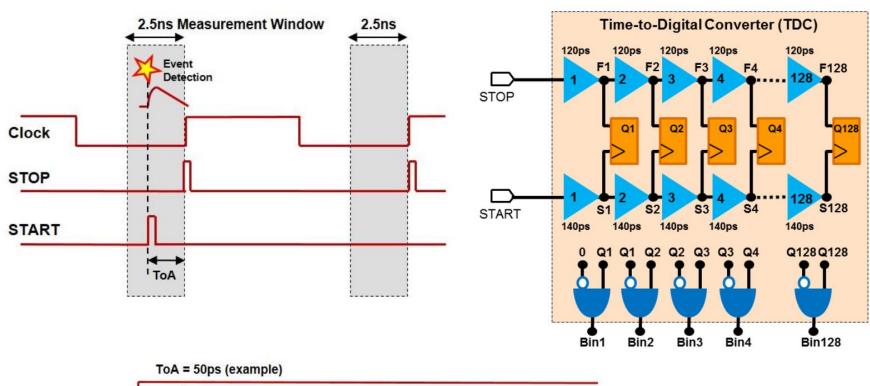

#### **TDC Bin Calibration**

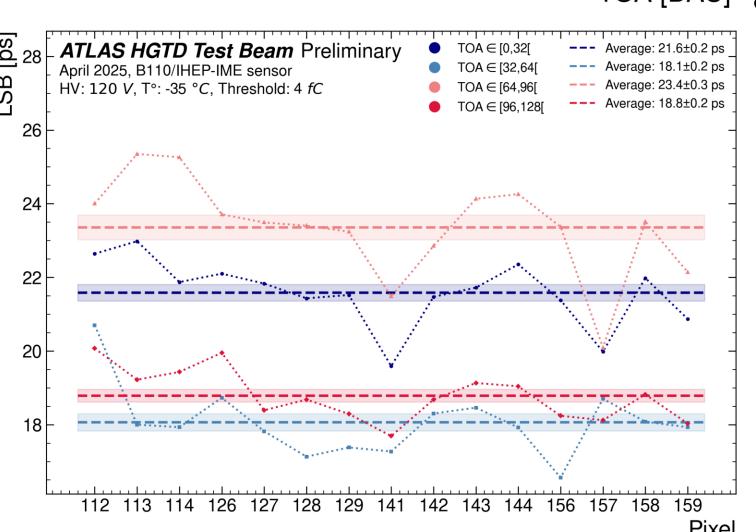

- Quantization error corresponds to the TDC quantization step size (or LSB, Least Significant Bit)

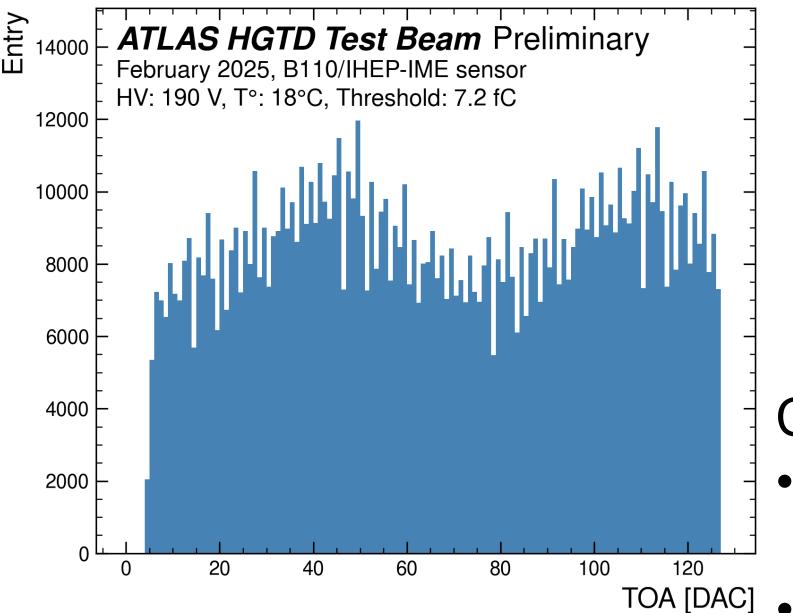

- Despite the nominal 20 ps LSB, non-linearity has been observed over the 128 TDC bins

- The LSB also depends on the temperature, and possibly the stability of power supply, and has to be calibrated

#### Calibration:

- Internal charge injection in ASIC

- Data-driven

calibration using

testbeam data

https://twiki.cern.ch/twiki/bin/view/AtlasPublic/HGTDTestBeamALTIROCA

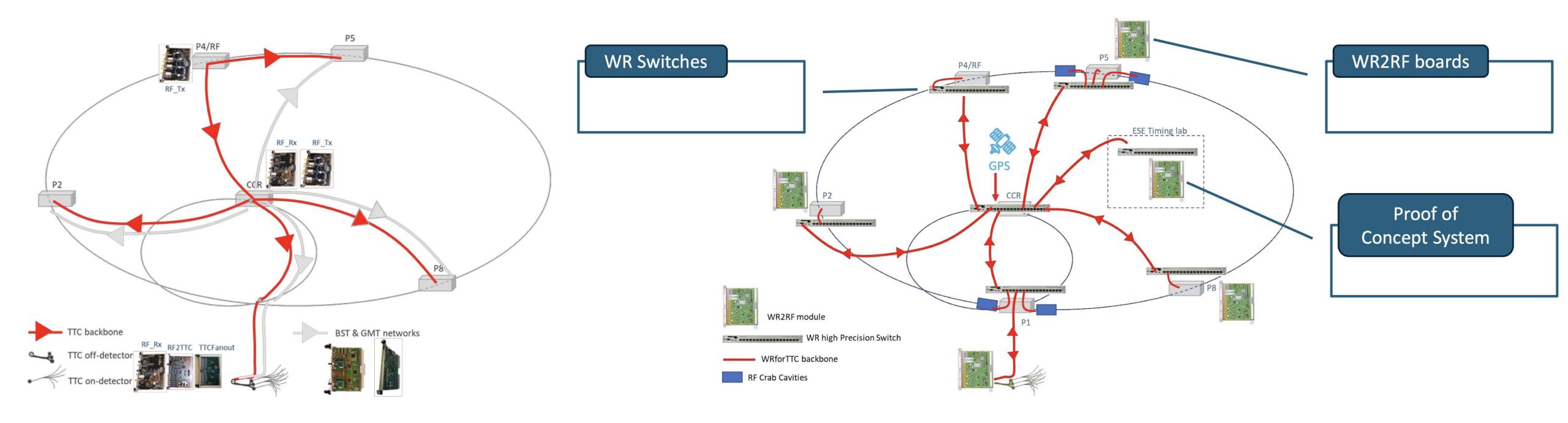

#### Clock

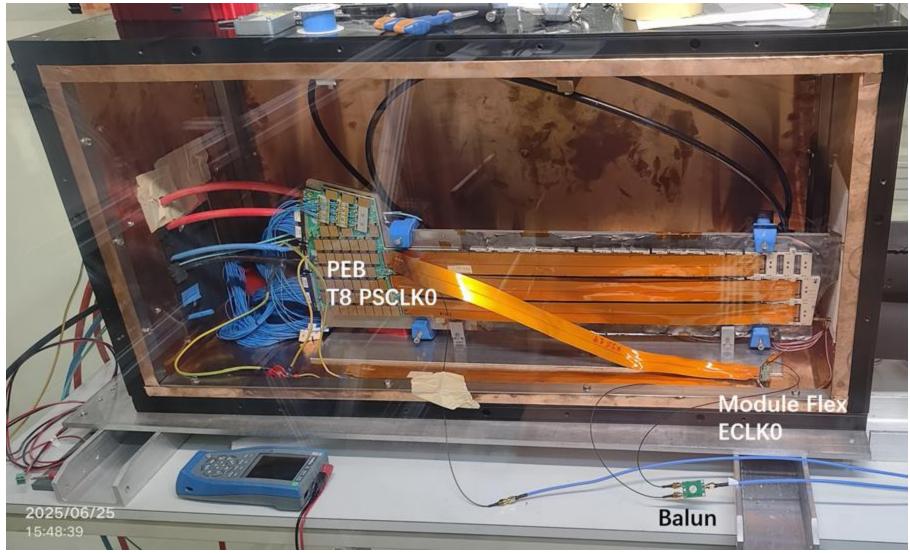

LTI→FELIX→VTRx+→lpGBT→Module Flex Phase difference between LTI and Module Flex

ATLAS Phase-II TTC tree LHC RF High-speed point-2-point bunch-clock 40.08 MHz optical serial bi-direct, links L0CT (AMD US+) USA15 LTI LTI LTI **ATCA** AMD / Intel **FPGAs** FLX FLX Fiber ~50m DFI DFI IPGBT IPGBT IPGBT Detector front-end Recovered bunch-clock

CTP: central trigger unit LTI: local trigger interface

ATL-DAQ-SLIDE-2024-456

~4 ps clock jitter if the temperature drift effect can be compensated

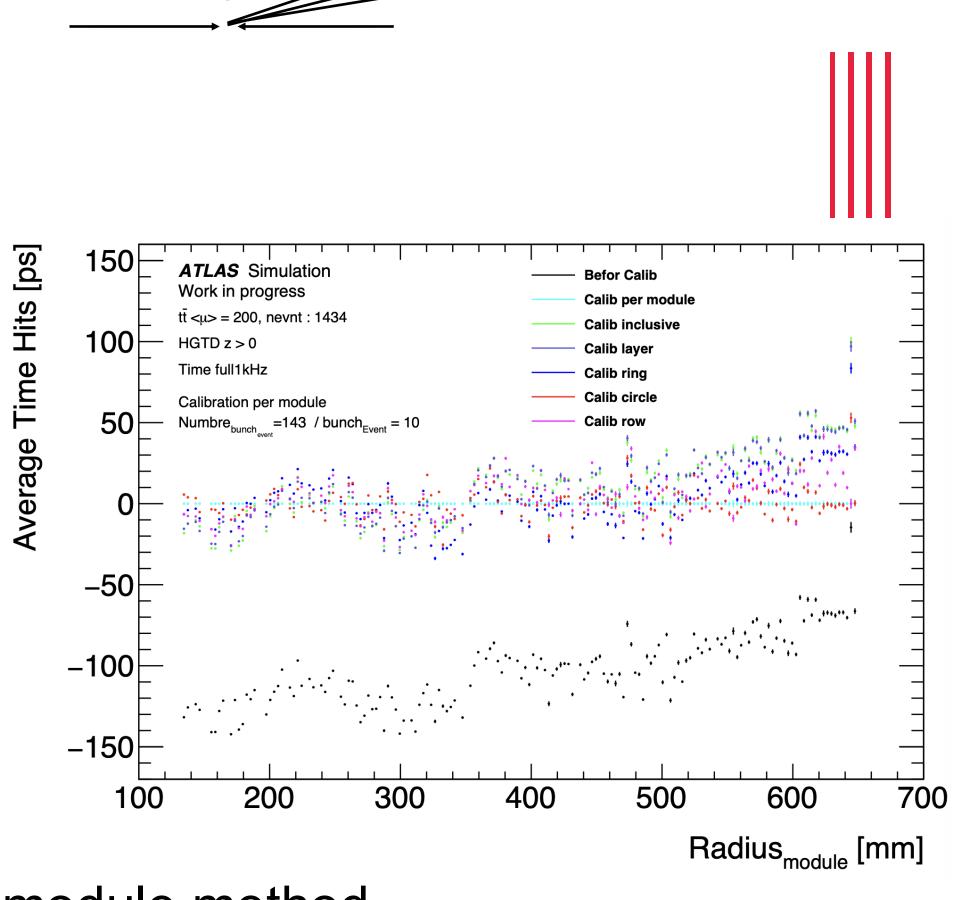

$$t_{\rm calib}(=t_0)=t_{\rm hits}-{\rm Calibration\ Constant}=t_{\rm hits}-\langle t_{\rm hit}\rangle$$

■ Calib. per circl: constants calibration per layer and circles defined by dR=40.

■ Calib. per row:

constants computed per

layer and per row, as

defined by the readout

1st disk 7984 modules

Front modules

Back modules

R = 120 mm

R = 320 mm

R = 660 mm

Constants calibration

is computed at level

of module.

■ Calib. per layer: constants calibration is computed at level of layer.

Calib. per inclusive: constants calibration is computed at level of 2 disks.

electronics <a href="https://conferences.slac.stanford.edu/sites/default/files/2023-09/Poster\_01\_Abdellah%20Tnourji.pdf">https://conferences.slac.stanford.edu/sites/default/files/2023-09/Poster\_01\_Abdellah%20Tnourji.pdf</a>

The ToF effect can be compensated using the calibration per module method

200

-200

-400

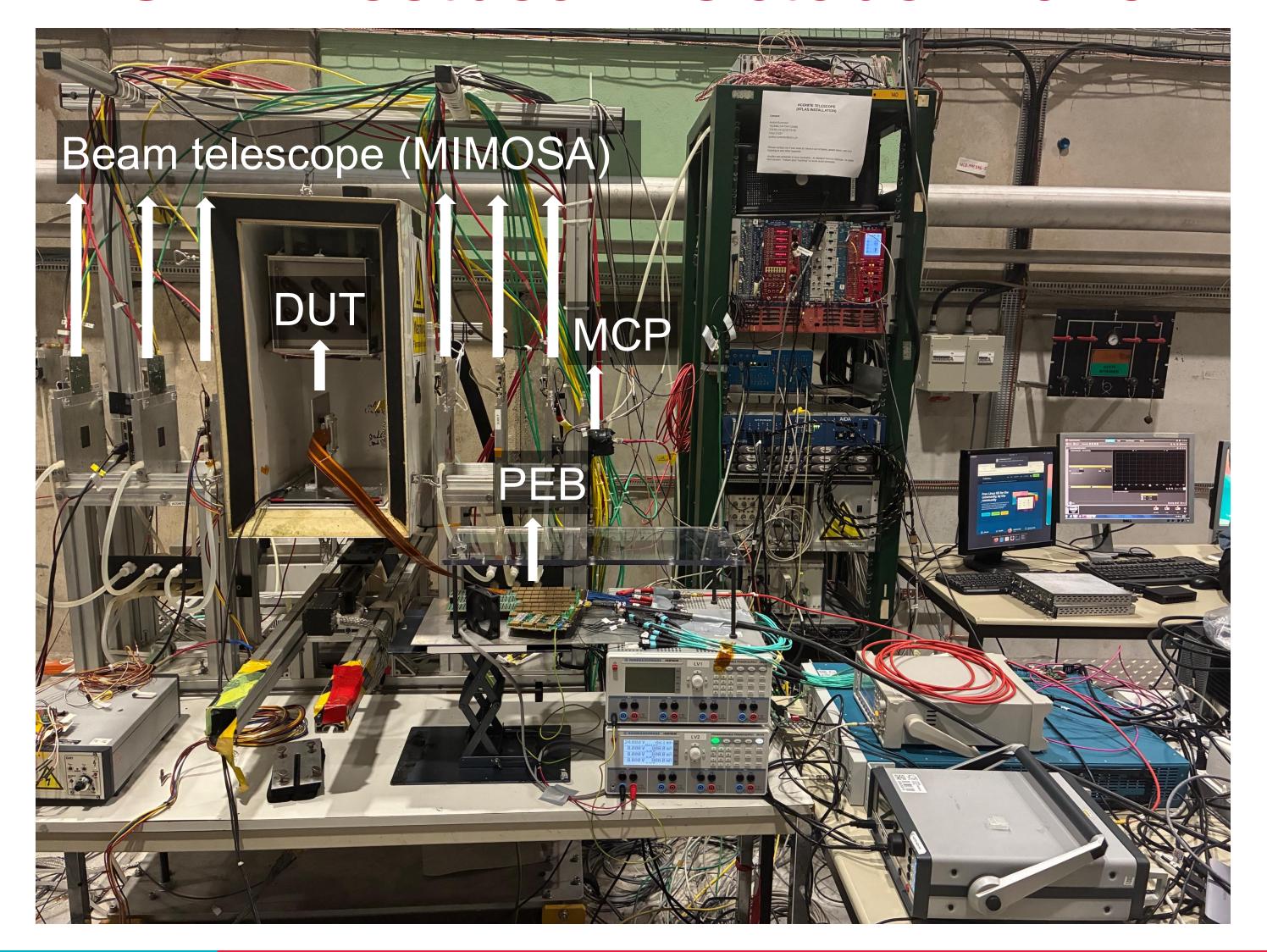

#### HGTD Testbeam October 2025

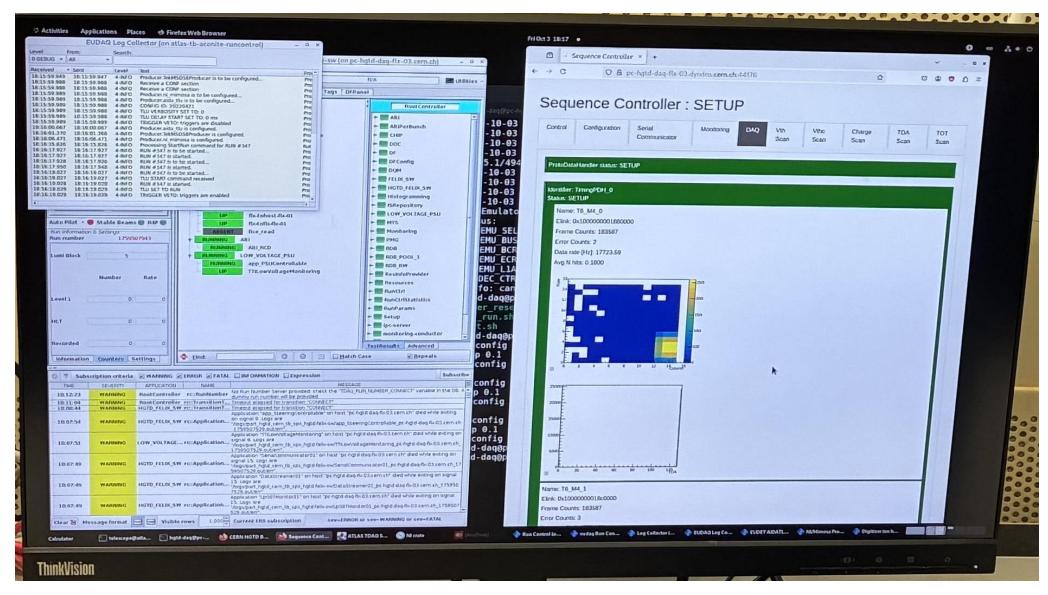

The first time reading out data using the HGTD online software through the Peripheral Electronics Board (PEB) and FELIX card

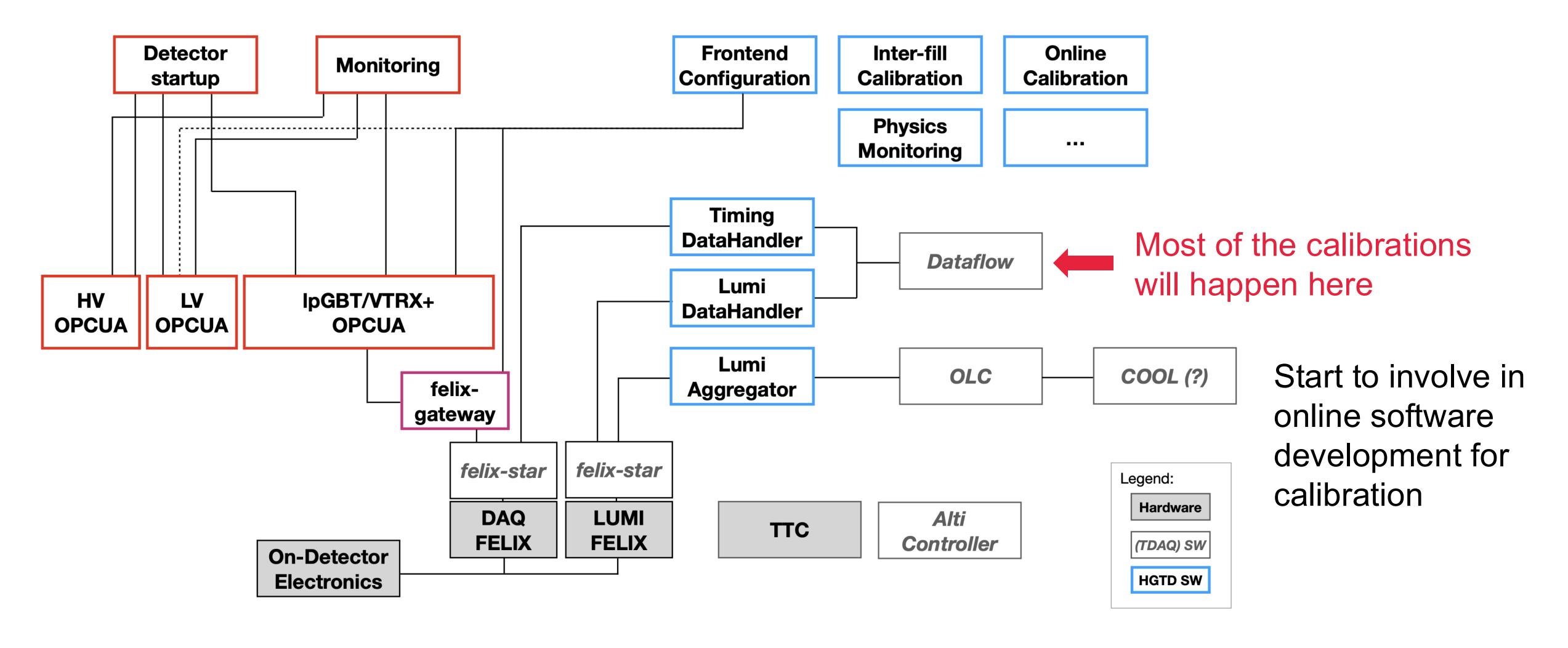

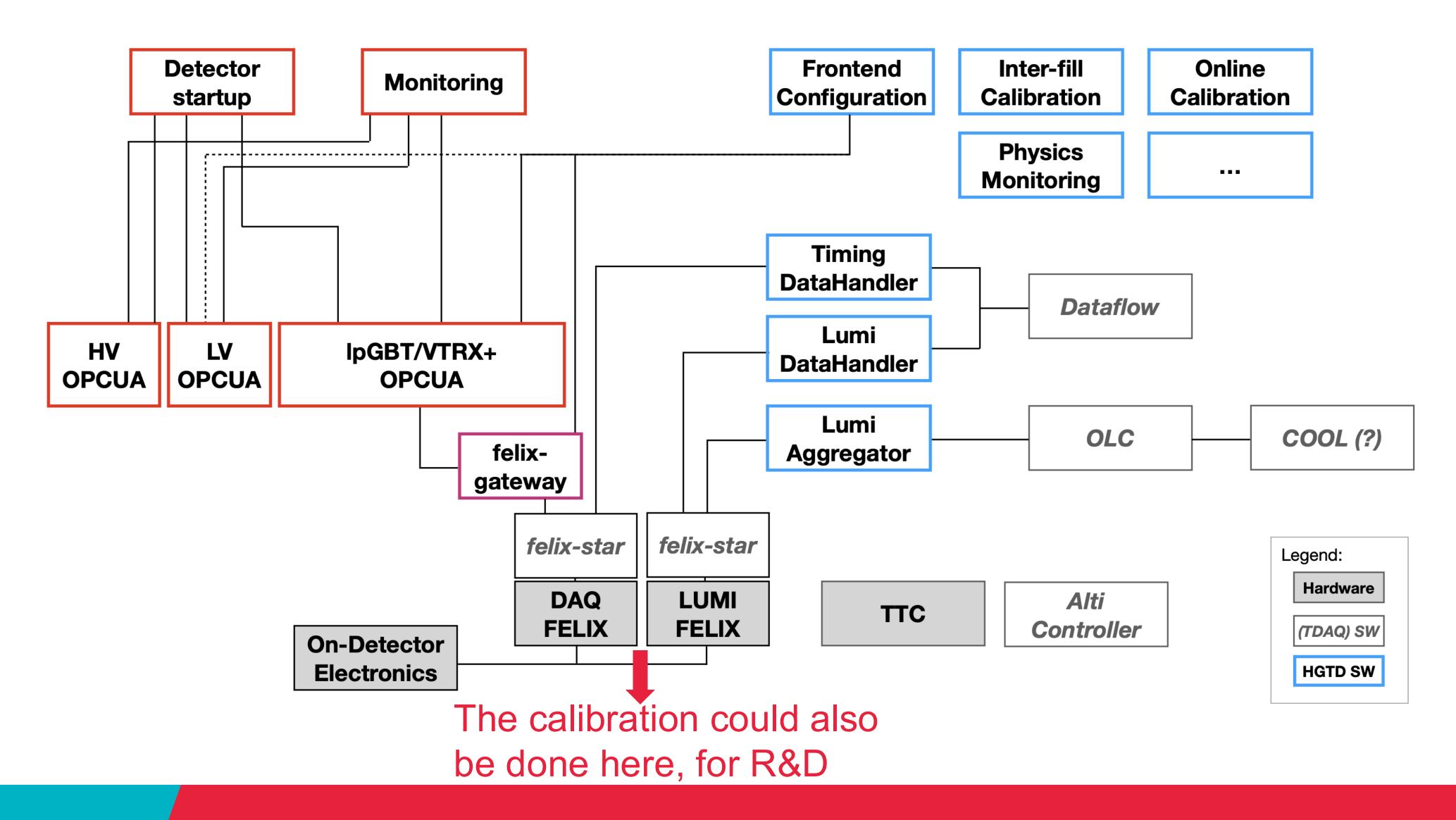

#### Calibration on HGTD Online Software

#### Calibration on FPGA

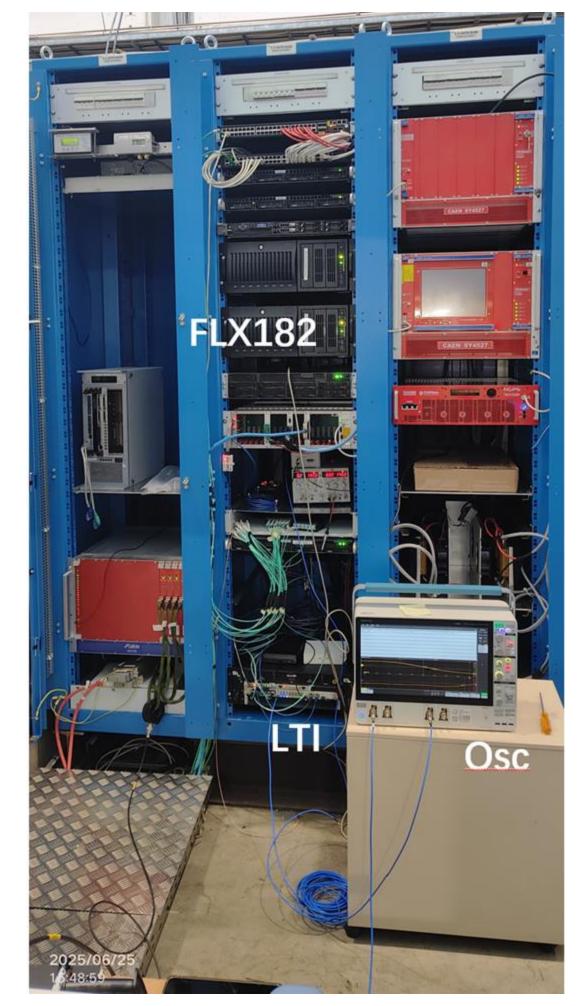

## Setup in Nijmegen | Replicate the setup at CERN

CERN setup

#### Plan

- Having a proper HGTD DAQ setup at Nijmegen to measure clock and timing, possibly also a beta source setup

- Analyse testbeam data to have better understanding of the module performance and the corresponding calibrations

- Involve in online software development and discover the feasibility of implementing the different calibration algorithms

- Once the calibration algorithms on the online software are in good shape, consider the possibility of implementing them using FELIX

## Thank you

## Backup

## Backup